Nghiệm thu đề tài cấp ĐHQG-HCM loại B tại Trường Đại học Bách khoa: Đồng thiết kế phần cứng phần mềm tăng tốc các mạng nơ-ron

|

1. |

Tên đề tài: | Đồng thiết kế phần cứng phần mềm tăng tốc các mạng nơ-ron |

| 2. | Mã số | B2021-20-02 |

| 3. | Chủ nhiệm đề tài: |

PGS.TS. Phạm Quốc Cường Nhóm nghiên cứu gồm: 04 PGS.TS, 03 TS, 01 ThS và 01 KS. |

| 4. | Đơn vị: | Trường Đại học Bách Khoa, ĐHQG-HCM |

| 5. | Lĩnh vực: | Công nghệ thông tin – truyền thông |

| 6. | Loại hình : | Nghiên cứu cơ bản |

| 7. | Thời gian thực hiện: |

24 tháng (2021-2023), gia hạn 06 tháng |

| 8. | Kinh phí nghiên cứu: | 940 triệu đồng |

| 9 | Thời gian nghiệm thu | 15 giờ, ngày 28 tháng 9 năm 2023 tại Phòng họp Khoa Khoa học và Kỹ thuật Máy tính, Trường Đại học Bách khoa, ĐHQG-HCM. |

| 10 | Chủ tịch Hội đồng và quyết định thành lập HĐ |

Quyết định 1186/QĐ-ĐHQG ngày 28/8/2023 của Giám đốc ĐHQG-HCM bao gồm các thành viên cụ thể như sau:

|

| 11. | Nội dung thực hiện |

– Nội dung 1: Phân tích đặc tính mạng nơ-ron học sâu . Kết quả: đã hoàn thành 01 Mô hình/công cụ phân tích thông tin các mạng nơ-ron học sâu nhằm thu được các thông tin về đặc tính khối lượng xử lý, thời gian xử lý và lượng dữ liệu truyền nhận giữa các giai đoạn tính toán của mạng nơ-ron; 01 Bảng báo cáo kết quả lựa chọn các giai đoạn tính toán sẽ hiện thực các lõi phần cứng chuyên biệt để tăng tốc trên FPGA; 01 Bảng báo cáo về các dịch vụ quản lý và điều khiển ở mức phần mềm cần hiện thực – Nội dung 2: Thiết kế tổng quan hệ thống tăng tốc mạng nơ-ron học sâu kết hợp các nền tảng tính toán . Kết quả: đã hoàn thành 01 Bảng thiết kế tổng quan hệ thống như đã nêu ở mục tiêu; 01 Bảng phân hoạch giai đoạn và nền tảng tính toán; 01 Bảng thiết kế về giao tiếp dữ liệu, chuẩn đồng bộ và bắt tay giữa các nền tảng tính toán; 01 Kết quả mô phỏng, phân tích bảng thiết kế trên các công cụ mô phỏng; Công bố 01 bài báo khoa học tại hội nghị quốc tế – Nội dung 3: Thiết kế và hiện thực các lõi tính toán phần cứng chuyên biệt . Kết quả: đã hoàn thành 01 Bảng thiết kế khả hiện thực với ngôn ngữ đặc tả phần cứng cho lõi tính toán chuyên biệt đã lựa chọn dựa trên giao thức truyền dữ liệu đã thiết kế; 01 Lõi phần cứng đã hiện thực bằng Verilog khả tổng hợp với một họ FPGA thương mại (Xilinx/Altera) và hoạt động được ở tần số tối thiểu 200 MHz; 01 Bảng kết quả mô phỏng, đánh giá và bảng phân tích số liệu tần số hoạt động, công suất và năng lượng tiêu thụ; 01 Hệ thống tích hợp các lõi phần cứng và CPU; 01 Báo cáo kết quả tích hợp và kết quả đánh giá độ chính xác và hiệu suất; 01 Bài báo khoa học đăng trong hội nghị quốc tế và 01 Bài báo khoa học tạp chí quốc tế. – Nội dung 4: Thiết kế và hiện thực các dịch vụ quản lý và điều khiển mức phần mềm . Kết quả: đã hoàn thành 01 Bảng thiết kế và mô tả giao thức quản lý và điều khiển dựa trên giao thức truyền dữ liệu; 01 Bảng thiết kế và đặc tả các dịch vụ cần thiết đã nêu; 01 Mã nguồn hiện thực các dịch vụ; 01 Báo cáo kết quả thử nghiệm và đánh giá khi hoạt động với các lõi phần cứng chuyên dụng; 01 Bài báo khoa học đăng ở tạp chí quốc tế miêu tả hệ thống phần cứng phần mềm hoàn chỉnh. – Nội dung 5: Phát triển ứng dụng kiểm thử (case study), so sánh đánh giá kết quả . Kết quả: đã hoàn thành 01 Hệ thống đã tích hợp hoàn chỉnh các nền tảng xử lý CPU, GPU và FPGA hoạt động đúng đắn; 01 Bảng báo cáo các kết quả thử nghiệm và đánh giá hoạt động của hệ thống với dữ liệu giả lập; 01 Bài báo khoa học công bố ở tạp chí quốc tế; 01 bảng mô tả nộp hồ sơ đăng ký giải pháp hữu ích – Nội dung 6: Tích hợp, mô phỏng và đánh giá toàn bộ hệ thống . Kết quả: 01 Ứng dụng kiểm thử phát triển dựa trên hệ thống xây dựng từ đề tài; 01 Báo cáo đánh giá kết quả xử lý, hiệu suất tính toán và các vấn đề liên quan; 01 Báo cáo đánh giá các điểm mạnh điểm yếu và các cơ hội phát triển hệ thống dựa trên kết quả thực nghiệm thực tế với ứng dụng cụ thể; 01 Bài báo được chấp nhận bởi một hội nghị khoa học quốc tế uy tín chuyên ngành bàn về việc phát triển ứng dụng trên hệ thống đã công bố. |

| 12. | Kết quả |

* Sản phẩm mềm: Lõi đặc tả phần cứng chuyên biệt dùng tăng tốc mạng nơ-ron trên phần cứng tái cấu hình; Bảng thiết kế hệ thống phần cứng phần mềm; dịch vụ quản lý và điều khiển mức phần mềm * Sản phẩm cứng: Không. * Sản phẩm đào tạo và khoa học: . 02 bài báo SCIE và Scopus Q2 trên tạp chí Electronics và tạp chí Mobile Networks and Applications . 03 bài báo Scopus Q3/Q4 trên các tạp chí Journal of Advances in Information Technology, Lecture Notes on Data Engineering and Communications Technologies, và Lecture Notes of the Institute for Computer Sciences, Social Informatics and Telecommunications Engineering . 01 bài báo trong hội nghị quốc tế thuộc danh mục Scopus: Advanced Technologies for Communication (ATC) . 01 bài báo tạp chí thuộc danh mục HĐGSNN: REV Journal on Electronics and Communication . Đào tạo: 03 thạc sỹ . 01 quyết định chấp nhận đơn hợp lệ giải pháp hữu ích |

| 13. | Hình ảnh giới thiệu kết quả |

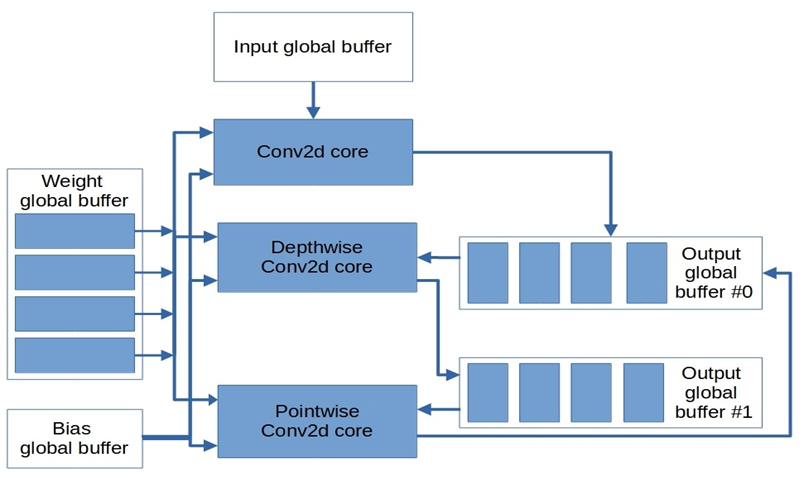

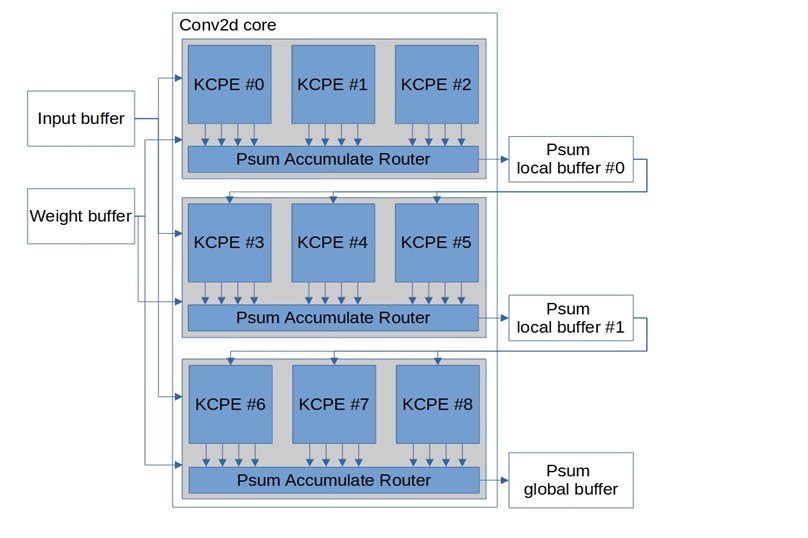

Lõi tăng tốc mạng nơ ron CNN

Kiến trúc khối tính tích chập 2 chiều (2D convolution) |

| 14. | Thông tin liên hệ CNĐT |

Email: cuongpham@hcmut.edu.vn Điện thoại: 0983846252 |

| 15. | Liên hệ ĐHQG-HCM | Ban Khoa học và Công nghệ (Phòng 309, NĐH) và Trang điện tử thông tin về hoạt động KH&CN (https://research.vnuhcm.edu.vn/) |

Trường ĐH Bách Khoa, ĐHQG-HCM